編輯點評:

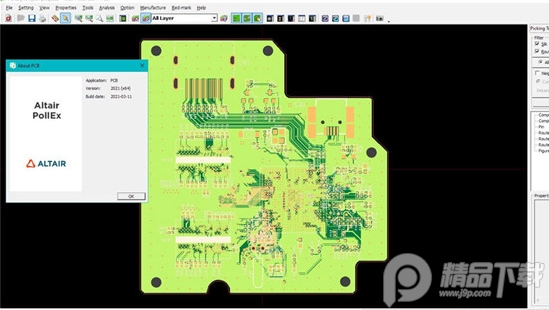

Altair PollEx2021破解補丁(附使用教程)是一款針對軟件Altair PollEx2021的破解工具,通過這款補丁可以幫助用戶一鍵激活破解軟件,這樣就可以免費使用這款軟件了

破解教程

1、下載解壓,得到軟件安裝文件和破解補丁;

2、運行hwPollEx2021_win64.exe開始安裝,然后同意條款;

3、選擇軟件安裝路徑,默認即可;

4、選擇創(chuàng)建快捷方式,方便之后運行;

5、等待安裝完成,點擊done退出引導(dǎo);

6、將破解補丁復(fù)制到軟件根目錄下,如圖所示;

默認路徑:C:\Program Files\Altair\2021\PollEx

7、軟件安裝完成,所有功能可免費使用

Altair PollEx應(yīng)用

1、統(tǒng)一零件庫

通用的統(tǒng)一零件庫支持所有設(shè)計過程,使來自不同學科的工程師能夠有效地協(xié)作進行項目,共享集中在一處的物理,邏輯,熱,電氣和裝配屬性數(shù)據(jù)。

2、原理圖設(shè)計審查

除行業(yè)中性格式外,PollEx還可以從所有主要ECAD供應(yīng)商(包括Cadence,Mentor Graphics,Zuken和Altium)導(dǎo)入設(shè)計。它的建模功能支持設(shè)計審查,包括原理圖和PCB數(shù)據(jù)之間的比較,因此可以在過程的早期發(fā)現(xiàn)并解決故障,而無需昂貴的ECAD許可證。

3、PCB審查,檢查和驗證

Pollex具有無與倫比的讀取主要ECAD文件格式的功能和易于使用的應(yīng)用程序,可促進從事原理圖和PCB設(shè)計的專家團隊的協(xié)作。改善電路板布局,并使用仿真工具來驅(qū)動設(shè)計,以實現(xiàn)信號完整性,電源完整性,EMI漏洞和ESD保護。

在BOM,邏輯和PCB級別上跟蹤并通知多學科團隊成員設(shè)計變更和修訂,導(dǎo)出驗證結(jié)果的智能文檔報告,并輕松共享設(shè)計更新文檔以始終保持最高的設(shè)計質(zhì)量。

4、PCB分析與優(yōu)化

除了內(nèi)置的分析功能外,PollEx還可以導(dǎo)出到其他Altair和第三方物理模擬工具。您可以利用Altair單元來利用我們的求解器來自信地識別和糾正開發(fā)早期的設(shè)計問題。使用Altair ElectroFlo?進行不需要高級CFD知識的早期熱分析。使用Altair SimLab?通過強大且可重復(fù)的工作流程自動執(zhí)行結(jié)構(gòu)應(yīng)力,振動和跌落測試性能,從而獲得快速,準確和一致的結(jié)果。使用Altair Feko?進行詳細的EMI / EMC分析。

5、制造設(shè)計

PollEx通過將制造,安裝,鑲板和測試數(shù)據(jù)導(dǎo)出到生產(chǎn)線機械來提高PCB生產(chǎn)效率。超過500種可制造性(DFM)設(shè)計檢查涵蓋了板,組件,鉆頭,F(xiàn)PCB,封裝,焊盤,圖案,放置和工具的制造領(lǐng)域。自動化和可定制的測試可以更早地發(fā)現(xiàn)潛在的可制造性問題并提高良率。

6、組裝和測試設(shè)計

PollEx提供了一套用于設(shè)計PCB的工具,同時考慮了易于組裝和線下測試的問題。避免了超過50種的裝配設(shè)計(DFA)檢查是否存在與碰撞,引線,放置,組件和電路板有關(guān)的裝配問題。

通過將制造,安裝,鑲板和測試數(shù)據(jù)導(dǎo)出到生產(chǎn)線機器,提高了PCB制造,組裝和線下測試的效率。

新版功能

1、添加功能以導(dǎo)出圖層圖像

PollEx PCB支持導(dǎo)出圖稿層和物理層的圖像。支持的格式為“ JPG和.BMP格式。可以從PollEx PCB中的文件-導(dǎo)出至-圖像菜單中使用此功能。

2、添加功能以支持LPDDR4分析

用于分析LPDDR4的功能,該功能已添加到PollEx SI的自動DDR總線分析功能中。 LPDDR4時序標準表已添加。

在現(xiàn)有的DDR技術(shù)中。 Vref yoltage,它是定時數(shù)據(jù)和地址總線的測量參考。用作固定值,但LPDDR4中的Vref電壓是通過訓練過程在IC內(nèi)部生成的。如果使用了使用分析結(jié)果提取Vref DQ選項,則以JEDEC指定的方式搜索Vref值。作為對所有IC的數(shù)據(jù)/地址總線的分析結(jié)果,可獲得最張開眼睛的電壓電平。 Vref值由它們的中間值確定。如果使用了“使用用戶定義的值”選項,則用戶可以設(shè)置所需的Vref值。

3、將Sl替換為HyperSpice引擎

PollEx SI的Spice引擎已從Polliwog Spice更改為HyperSPICE,因為只有Spice引擎在同一用戶GUI的內(nèi)部進行了更改。但是,默認的Spice Control參數(shù)已更改

4、添加阻抗圖的特征

添加了在PollEx DFE +的阻抗檢查項目的結(jié)果中顯示阻抗圖的功能。 在結(jié)果表中單擊“阻抗圖”按鈕后執(zhí)行阻抗檢查后,將顯示“阻抗圖”對話框。 通過使用此菜單,用戶可以輕松找到整個BUS整個路徑中的阻抗失配區(qū)域。

5、添加串擾耦合表映射功能

添加了在PollEx DFE +的“串擾噪聲”檢查項目的結(jié)果中顯示“后向串擾系數(shù)(kb)”耦合圖的功能。 在結(jié)果表中單擊“耦合圖”按鈕后執(zhí)行“串擾噪聲”檢查后,將顯示“耦合圖”對話框。 通過使用此菜單,用戶可以輕松找到整個BUS整個路徑中串擾容易受到影響的區(qū)域。

6、添加電源完整性檢查功能

PollEx DFE +中增加了檢查功率飽和度的功能。 新添加的功能是IR下降,環(huán)路電感和PDN阻抗

IR-Drop Check:IR下降是指出現(xiàn)在電網(wǎng)電阻組件上的電壓下降。 IR降是電流流動期間電源與負載組件之間的電位差。 如果提供給普通的電壓電平是。

由于IR-Drop而上升。 系統(tǒng)出現(xiàn)故障或唾液的Risina / Fallina時間不正確。 導(dǎo)致信號完整性問題。 因此,為了使組件正常工作,有必要檢查IR-Drop的量是否在組件允許的極限值之內(nèi)。此項檢查指定組件的電壓電平是否低于指定電平。

回路電感檢查:在PCB中。 電源線通常是指連接電源(VRM)和負載組件的電源網(wǎng)絡(luò)。

這些電源走線配置的特性可以通過PCB的電源傳輸網(wǎng)絡(luò)(PDN)來確定,PDN的運行就像無源組件(例如線圈或電容器)一樣。 取決于其物理性質(zhì)。 由于這些鼻孔成分而產(chǎn)生諧振,并且流過諧振結(jié)構(gòu)的電流會引起局部失真和FM問題,通常應(yīng)將PDN阻抗設(shè)計得盡可能低,通常是為了使PDN阻抗低。 在電源引腳周圍安裝了一個去耦電容器。 為了使該去耦合電容器有效工作,必須將電源引腳和去耦電容器之間的環(huán)路電感設(shè)計為較小。此項檢查電源引腳和去耦合電容器之間的傾斜電感是否超過用戶指定的值。

PDN阻抗檢查:在PCB中,電源線通常是指連接電源(VRM)和負載組件的電源網(wǎng)絡(luò)。

這些電源走線配置的特性可以通過PCB的電源傳輸網(wǎng)絡(luò)(PDN)來確定。 根據(jù)其物理特性,PDN的工作方式類似于無源組件,例如線圈或電容器。 由于這些無源元件而產(chǎn)生諧振,并且流過諧振結(jié)構(gòu)的電流會引起弦失真和EMI問題。 因此,在設(shè)計階段對PDN阻抗的精確分析非常重要。

此項檢查指定電源引腳的PDN阻抗是否高于用戶指定的目標阻抗。

7、添加功能以導(dǎo)出熱結(jié)果

在PollEx Thermal中,添加了以標準文件格式輸出熱分析結(jié)果的功能。 分析結(jié)果可以Excel格式或格式輸出。 CSV格式。 在“熱分析”對話框中,使用“文件/導(dǎo)出到CSV”菜單,用戶可以生成結(jié)果文件。 分析結(jié)果之中。 PCB頂部/底部表面溫度將保存為desianname頂部/底部。 xlsx文件,保存的格式是X Y坐標和溫度值。 組分溫度另存為設(shè)計名稱Component。 xlsx文件,保存的格式是“參考名稱”。 PlaceLaver.XY坐標和溫度值。

office2021 正式版

office2021 正式版 Office 2021 LTSC版

Office 2021 LTSC版 搜狗輸入法電腦版

搜狗輸入法電腦版 Adobe Acrobat PRO DC最新訂閱版

Adobe Acrobat PRO DC最新訂閱版 蘋果iTunes官方正版

蘋果iTunes官方正版 PDF Shaper Professional破解版

PDF Shaper Professional破解版 極品五筆輸入法2.2最新版

極品五筆輸入法2.2最新版 搜狗五筆輸入法最新版

搜狗五筆輸入法最新版 手心輸入法官方PC版

手心輸入法官方PC版 7-Zip解壓軟件電腦版

7-Zip解壓軟件電腦版

輕松礦工挖礦軟件偷算力最新版4.3.4免費版

輕松礦工挖礦軟件偷算力最新版4.3.4免費版 青松守護(手機電腦監(jiān)管軟件)0.1.57155最新版

青松守護(手機電腦監(jiān)管軟件)0.1.57155最新版 永中PDF工具集(PDF文檔轉(zhuǎn)換)1.0.0免費版

永中PDF工具集(PDF文檔轉(zhuǎn)換)1.0.0免費版 好易迅轉(zhuǎn)寫專家vip破解免費版4.6.1免激活版

好易迅轉(zhuǎn)寫專家vip破解免費版4.6.1免激活版 小滑板英語學習軟件免費下載1.20.02最新版

小滑板英語學習軟件免費下載1.20.02最新版 華師云課堂教學平臺最新版3.0.0.50免費版

華師云課堂教學平臺最新版3.0.0.50免費版 ObjectDock Plus仿蘋果桌面軟件下載2.2綠色版

ObjectDock Plus仿蘋果桌面軟件下載2.2綠色版 新東方比鄰?fù)饨屉娔X版1.27.0.786最新版

新東方比鄰?fù)饨屉娔X版1.27.0.786最新版 2345PicViewer.exe優(yōu)化版下載10.3.1.9124免費版

2345PicViewer.exe優(yōu)化版下載10.3.1.9124免費版 老年人能力評估管理系統(tǒng)下載1.0免費版

老年人能力評估管理系統(tǒng)下載1.0免費版 TrenGIF插件GIF表情包在線生成器下載1.0.0免費版

TrenGIF插件GIF表情包在線生成器下載1.0.0免費版 支付寶紅包頁面生成器1.0綠色版

支付寶紅包頁面生成器1.0綠色版 小黑課堂計算機二級Office題庫2022新版5.6.7 免費版

小黑課堂計算機二級Office題庫2022新版5.6.7 免費版 今日制造免積分會員版1.0.0.69 免費版

今日制造免積分會員版1.0.0.69 免費版 超星爾雅答案查詢助手1.0智慧樹答案

超星爾雅答案查詢助手1.0智慧樹答案 眼睛視力盲區(qū)及弱視度測試軟件1.0.0免費版

眼睛視力盲區(qū)及弱視度測試軟件1.0.0免費版 MindMapper21注冊機下載21.0免費版

MindMapper21注冊機下載21.0免費版 轉(zhuǎn)易俠PDF轉(zhuǎn)換器免費下載3.7.0.1509最新版

轉(zhuǎn)易俠PDF轉(zhuǎn)換器免費下載3.7.0.1509最新版 通用文件瀏覽器Universal View Pro下載6.7.8.0單文件綠色版

通用文件瀏覽器Universal View Pro下載6.7.8.0單文件綠色版 nb物理實驗室最新版下載5.5.9 官方版

nb物理實驗室最新版下載5.5.9 官方版 mathworks matlab r2021a破解補丁免費版中文完美授權(quán)破解

mathworks matlab r2021a破解補丁免費版中文完美授權(quán)破解 大小: 16.4M

大小: 16.4M

小說寫作助手

小說寫作助手 日歷模板電子版

日歷模板電子版 pdf編輯器免費版

pdf編輯器免費版 支持拼音的輸入法軟件

支持拼音的輸入法軟件 PDF閱讀器電腦版

PDF閱讀器電腦版 LSV全球高清地圖衛(wèi)星下載器

LSV全球高清地圖衛(wèi)星下載器

小學生口算題卡生成器最新版

小學生口算題卡生成器最新版

熱門評論

最新評論